晶圓背面減薄技術是半導體制造中的關鍵工藝之一,其核心目的是通過物理或化學方法將晶圓背面材料去除至特定厚度,以滿足芯片封裝、性能優化及成本控制等多重需求。這一技術貫穿于集成電路制造的中后段,尤其在三維集成、先進封裝等領域扮演著不可替代的角色。以下從技術原理、應用場景及行業趨勢三個維度展開分析。

一、技術原理:從機械研磨到先進蝕刻的演進

晶圓減薄主要通過機械研磨(Grinding)、化學機械拋光(CMP)和干法蝕刻(Dry Etching)三類工藝實現。傳統機械研磨采用金剛石砂輪以每分鐘數萬轉的速度切削硅材料,可將12英寸晶圓從初始775μm減至50-100μm,但會引入表面應力微裂紋。為消除損傷層,業界開發了"粗磨+精磨+濕法蝕刻"的復合工藝,如東京精密開發的超精密研磨設備可將厚度偏差控制在±2μm以內。而針對10μm以下的極致減薄需求,等離子體蝕刻技術通過SF6/O2混合氣體實現各向同性刻蝕,配合激光剝離(Laser Lift-off)技術,已能實現5μm以下的超薄芯片制造。

值得注意的是,減薄過程中需同步解決翹曲控制問題。當300mm晶圓厚度低于50μm時,其剛度下降導致傳輸過程中易發生碎裂。應用材料公司開發的臨時鍵合/解鍵合(Temporary Bonding/ Debonding)系統,采用紫外固化膠將晶圓固定在玻璃載板上,使超薄加工成為可能。這種技術組合使得臺積電在InFO-WLCSP封裝中實現了25μm的硅中介層量產。

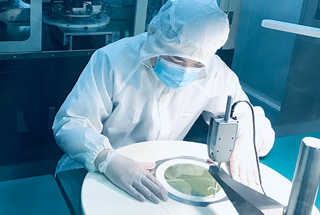

請點擊輸入圖片描述(最多18字)

二、應用場景:從傳統封裝到三維集成的需求升級

1. 封裝厚度控制:在QFN、BGA等傳統封裝中,減薄至150-200μm可顯著降低封裝體高度。日月光的數據顯示,每減少100μm厚度,手機主板空間利用率提升15%。但更革命性的突破發生在2.5D/3D封裝領域,如HBM內存堆疊要求每個DRAM芯片減薄至30μm,通過TSV實現8層堆疊后總厚度仍控制在700μm以內。

2. 熱管理優化:英特爾在Foveros 3D封裝中采用背面減薄至20μm結合微凸塊(μBump)技術,使邏輯芯片與存儲器的垂直間距縮短至50μm,熱阻降低40%。特別在GaN功率器件中,將SiC襯底減薄至80μm可使熱導率提升3倍,這對電動汽車逆變器模塊的散熱至關重要。

3. 柔性電子突破:索尼開發的CIS芯片通過背面減薄至5μm實現60°彎曲半徑,應用于內窺鏡成像模組。而柔性顯示驅動IC更需要將硅基板減薄至3μm以下,這要求開發新型載體薄膜材料以防止加工斷裂。

三、行業趨勢:材料創新與工藝融合

當前減薄技術正面臨兩大挑戰:一是硅基材料接近物理極限,當厚度低于10μm時載流子遷移率急劇下降;二是異質集成需求催生新工藝。imec正在研究將晶圓級石墨烯作為停止層,實現1μm級硅薄膜的精確控制。而針對第三代半導體,激光隱形切割(Stealth Dicing)與減薄工藝的協同可將SiC晶圓加工成本降低30%。

在中國大陸,中芯紹興建設的8英寸SiC生產線首次實現背面減薄與TSV工藝集成,使模塊導通電阻下降至2mΩ·cm²。長電科技開發的"減薄-穿孔-電鍍"一體化設備,更是將加工周期從傳統72小時壓縮至8小時。根據Yole預測,到2028年全球晶圓減薄設備市場規模將達47億美元,其中超薄加工(<50μm)占比將超過60%。

從更宏觀視角看,減薄技術正在重塑半導體產業格局:一方面使摩爾定律在封裝層面得以延續,另一方面推動芯片從平面走向立體。未來隨著光子集成、量子器件的興起,原子級精度減薄工藝或將開啟新的技術紀元。正如臺積電研發副總余振華所言:"晶圓減薄已從單純的尺寸縮減,進化為系統級性能優化的戰略工具。"這一技術的持續創新,將成為突破"內存墻""功耗墻"的關鍵支點。